**MT88V32**

August 1993

# 8 x 4 High Performance Video Switch Array

**Preliminary Information**

### Features

- 32 bidirectional CMOS "T" switches in an 8×4 non-blocking array

- Break-before-make switching configuration

- Fast setup & hold times for switch programming

- 3dB bandwidth of 200MHz

- Low feedthrough and crosstalk, better than -80dB at 5MHz

- Very low differential gain and phase errors

- 12Vpp bipolar signal capability

- On-state resistance 75 $\Omega$  (max) for V<sub>DD</sub>=+5V, V<sub>EE</sub>=-7V

- Switch control through 2-stage latches

- Orthogonal Xi and Yi pin connections for optimized PCB layout

- Latch readback capability for monitoring

## Applications

- High-end video routing and switching

- Medical instrumentation

- Automatic test equipment (ATE)

- Multi-media communication

Ordering Information MT88V32AP 44 Pin PLCC -40° to 85°C

**ISSUE 1**

#### Description

The MT88V32 is a digitally programmable (TTL levels)  $8\times4$  crosspoint switch that is designed to control wide-band analog (video) signal.

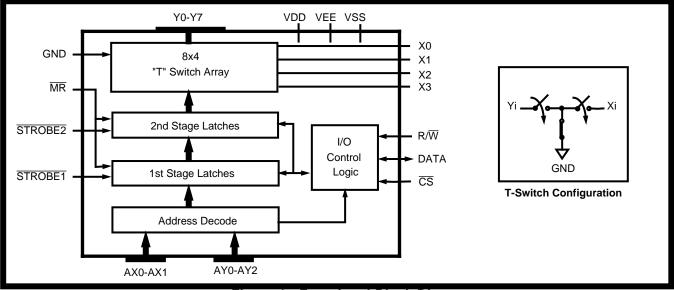

Each of the 32 nodes of the switching matrix has a Tswitch, see Fig.1. This grounds the nodes of all open connections, which greatly reduces feedthrough noise. In order to reduce crosstalk, individual analog signal lines are isolated by interleaving them with ground lines.

The two stage programmable latch system allows the state of all switching nodes to be updated simultaneously. The next state of the switch is written into the first stage of the latches through individual write cycles. These changes will not affect the current state of the switch. The STROBE2 control input is used to load the state of all first stage latches to the second stage latches, which updates the complete matrix. Therefore, all 32 switching nodes are updated simultaneously.

The MT88V32 supports separate analog ( $V_{EE}$ ) and digital ( $V_{DD}$ ) voltage references. This allows the user to select an optimum analog signal bias point.

Figure 1 - Functional Block Diagram

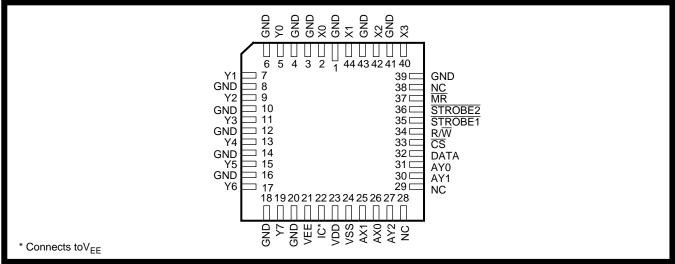

Figure 2 - Pin Connections

## **Pin Description**

| Pin #*                                                           | Name                                   | Description                                                                                                                                                                                                                         |

|------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 4, 6,<br>8, 10,<br>12, 14,<br>16, 18,<br>20, 39,<br>41, 43 | GND                                    | <b>Analog Ground.</b> Connect to system ground for crosstalk noise isolation. Pins 3 and 39 are not bonded internally.                                                                                                              |

| 2, 44,<br>42, 40                                                 | X0, X1,<br>X2, X3                      | Analog Lines (input/output).                                                                                                                                                                                                        |

| 5, 7,<br>9, 11,<br>13, 15,<br>17, 19                             | Y0, Y1,<br>Y2, Y3<br>Y4, Y5,<br>Y6, Y7 | Analog Lines (input/output).                                                                                                                                                                                                        |

| 21                                                               | V <sub>EE</sub>                        | Negative Analog Power Supply.                                                                                                                                                                                                       |

| 22                                                               | IC                                     | Internal Connection.                                                                                                                                                                                                                |

| 23                                                               | V <sub>DD</sub>                        | Positive Power Supply.                                                                                                                                                                                                              |

| 24                                                               | V <sub>SS</sub>                        | Digital Ground Reference.                                                                                                                                                                                                           |

| 25, 26                                                           | AX1,AX0                                | X0-X3 I/O Address Select (inputs).                                                                                                                                                                                                  |

| 27, 30,31                                                        | AY2-AY0                                | Y0-Y7 I/O Address Select (inputs).                                                                                                                                                                                                  |

| 28, 29                                                           | NC                                     | No Connection.                                                                                                                                                                                                                      |

| 32                                                               | DATA                                   | <b>DATA (input/output)</b> . When input, a logic high will close the selected switch and a logic low will open the selected switch. When output, a logic high indicates a closed switch and a logic low indicates an opened switch. |

| 33                                                               | CS                                     | Chip Select (input). Active low.                                                                                                                                                                                                    |

| 34                                                               | R/W                                    | <b>READ/WRITE Control (input).</b> When high the DATA pin is an output (for reading from second stage latch); when low the DATA pin is an input (for writing to first stage latch).                                                 |

| 35                                                               | STROBE1                                | <b>STROBE 1 (input).</b> Modifies memory content of first stage latch as determined by the addess and data lines, but does not change the switch array configuration of entire switch array. Active low.                            |

| 36                                                               | STROBE2                                | <b>STROBE 2 (input).</b> Transfers memory content of first stage latch to the second stage latch and hence, changes the configuration of entire switch array. Active low.                                                           |

| 37                                                               | MR                                     | MASTER RESET (input). Used to reset the first and second stage latches. Active low.                                                                                                                                                 |

| 38                                                               | NC                                     | No Connection.                                                                                                                                                                                                                      |

# **Functional Description**

The state of the MT88V32 8 X 4 switching matrix is updated through a simple parallel processor interface. This interface provides access to 32 two stage latches, which determines the state (open/ close) of each switching array node. Each latch (or node) is addressed by the AX0-AX1 and AY0-AY2 inputs as per Table 2, and the DATA input will determine if the connection is to be made (DATA=1) or opened (DATA=0).

The second stage of the two stage latches controls the current state of each switching node. The value held in the first stage is the input to the second stage. This allows the device to be programmed in two ways. That is, individual switching nodes may be updated one at a time, or all nodes may be updated at once.

To update one node at a time the STROBE2 input should be held low. This makes the second stage latches transparent and the matrix immediately reflects the state of the first stage latches. A write cycle example follows:

- 1) STROBE2 is low,

- 2)  $\overline{\text{CS}}$  and  $R/\overline{W}$  are low,  $\overline{\text{MR}}$  is high,

- 3) AX0-AX1 and AY0-AY2 as per Table 2,

- 4) DATA input high to close or low to open, and

- 5) **STROBE1** toggled from high-to-low-to-high.

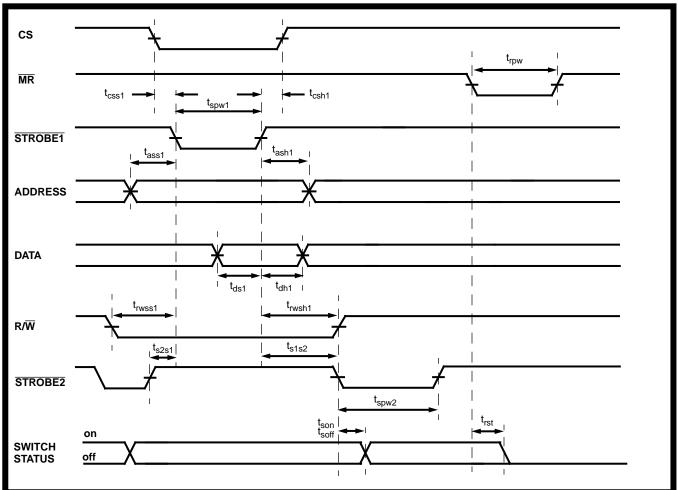

These steps (one write cycle) may be repeated for each switch state change. This can also be accomplished by holding STROBE1 low and toggling STROBE2. See Figure 14 for timing.

To update all nodes simultaneously all switch state changes must be written into the first stage latches. This is accomplished by holding STROBE2 high and performing steps 2) through 5) above for each switching node that is to be changed. Writing to the first stage latches only will not affect the switching state of the matrix. When the changes have been made all the switches of the matrix may be updated simultaneously by toggling the STROBE2 input from high-to-low-to high.

When STROBE2 is used to update the state of the MT88V32 all switch "breaks" are completed before any switch "makes" occur. There is approximately 10ns delay between "breaks" and "makes".

Both the first and second stage latches will be cleared when the master reset ( $\overline{MR}$ ) is taken from high-to-low. This will open all the switch nodes. The operation of  $\overline{MR}$  is independent of  $\overline{CS}$ , AX0-AX1, AY0-AY2 and R/ $\overline{W}$ .

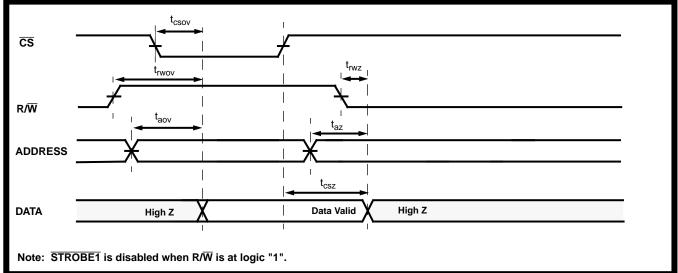

The status of each switching array node (second stage latch) can be read through the bidirectional DATA pin. A read cycle example follows:

- 1)  $\overline{\text{CS}}$  is low,  $R/\overline{W}$  and  $\overline{\text{MR}}$  are high,

- 2) AX0-AX1 and AY0-AY2 as per Table 2, and

- 3) DATA output high for closed or low for open.

| MR     | R/W    | CS     | DATA                                 | STROBE1                              | STROBE2                | DATA                                                                                                             |

|--------|--------|--------|--------------------------------------|--------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------|

| 1<br>1 | 0<br>0 | 1<br>0 | 0<br>1                               | $1 \rightarrow 0 \\ 1 \rightarrow 0$ | 1<br>1                 | No Change to 1st stage latch.<br>1st stage latch is loaded with data.                                            |

| 1<br>1 | 0<br>0 | 0<br>0 | $0 \\ 1 \rightarrow 0 \rightarrow 1$ | 0<br>0                               | 1<br>1                 | 1st stage latch is transparent.<br>Selected latch is cleared and set again (i.e.,<br>output follows input).      |

| 1<br>1 | 0<br>0 | 0<br>x | 1<br>x                               | $0 \rightarrow 1$<br>1               | $1 \\ 1 \rightarrow 0$ | 1st stage latch output is frozen.<br>Output of 1st stage latch is transferred to<br>output of 2nd stage latches. |

| 1<br>1 | 0<br>0 | x<br>0 | x<br>x                               | 1<br>0                               | 0→1<br>0               | 2nd stage latch output is frozen.<br>Both 1st stage and 2nd stage latches are<br>transparent.                    |

| 1      | 1      | 0      | 0                                    | x                                    | x                      | DATA becomes an output and reflects the contents of the 2nd stage latch addressed by AX0-AX1 and AY0-AY2.        |

| 0      | 1      | 1      | 1                                    | 1                                    | 1                      | All crosspoints opened (data in 1st and 2nd stage latches are cleared).                                          |

#### Table 1 - Truth Tables

Note: x = don't care, 0 = logic "0" state, 1 = logic "1" state A logic 1 on DATA input closes a connection. A logic 0 on DATA input opens a connection.

| AX1                                  | AX0                                  | AY2                             | AY1                                  | AY0                             | Switch Connections                                                                           |

|--------------------------------------|--------------------------------------|---------------------------------|--------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------|

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | Y0 to X0<br>Y1 to X0<br>Y2 to X0<br>Y3 to X0<br>Y4 to X0<br>Y5 to X0<br>Y6 to X0<br>Y7 to X0 |

| 0                                    | 1                                    | 0                               | 0                                    | 0                               | Y0 to X1                                                                                     |

| ↓                                    | ↓                                    | ↓                               | ↓                                    | ↓                               | ↓                                                                                            |

| 0                                    | 1                                    | 1                               | 1                                    | 1                               | Y7 to X1                                                                                     |

| 1                                    |                                      | 0                               | 0                                    | 0                               | Y0 to X2                                                                                     |

| ↓                                    |                                      | ↓                               | ↓                                    | ↓                               | ↓                                                                                            |

| 1                                    |                                      | 1                               | 1                                    | 1                               | Y7 to X2                                                                                     |

| 1                                    | 1                                    | 0                               | 0                                    | 0                               | Y0 to X3                                                                                     |

| ↓                                    | ↓                                    | ↓                               | ↓                                    | ↓                               | ↓                                                                                            |

| 1                                    | 1                                    | 1                               | 1                                    | 1                               | Y7 to X3                                                                                     |

| Table 2 - | Address | Decode | Truth | Table |

|-----------|---------|--------|-------|-------|

|           | ////    | Doodao |       | IUNIC |

It should be noted that the STROBE1 function is disabled during a read cycle. See Fig. 15 for timing.

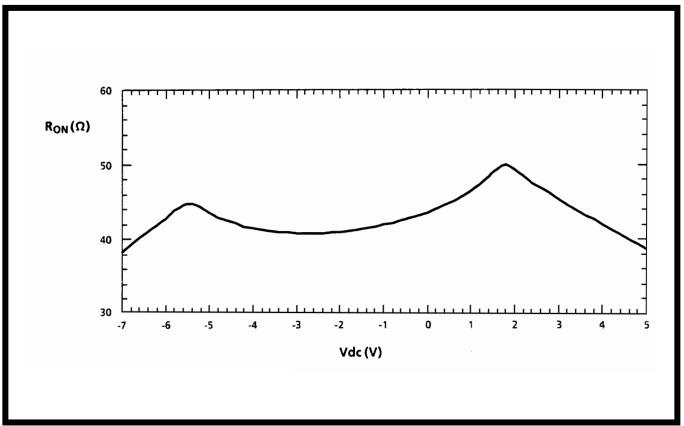

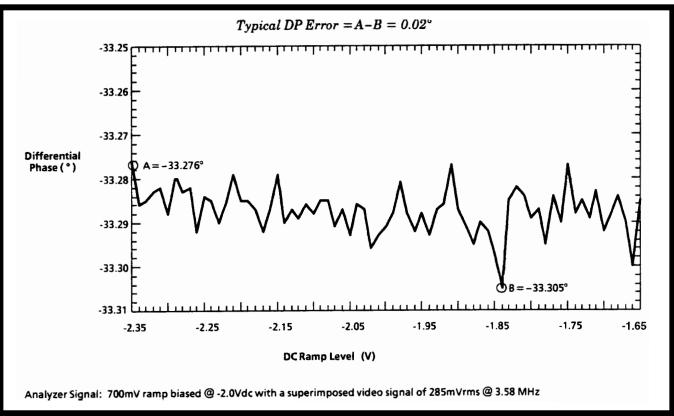

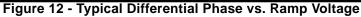

The MT88V32 can operate from a dual rail power supply ( $V_{DD}$  and  $V_{EE}$ ) or a single rail power supply ( $V_{SS}=V_{EE}=0V$ ) as per the recommended operating conditions. For minimum on-state resistance the supply voltages should be  $V_{DD}=5.0 V_{DC}$ ,  $V_{SS}=0 V_{DC}$  and  $V_{EE}=-7 V_{DC}$ . The analog input signal should be biased at -2.0  $V_{DC}$  to achieve minimum differential phase and gain error (see AC Electrical Characteristics - Crosspoint Performance).

# Applications

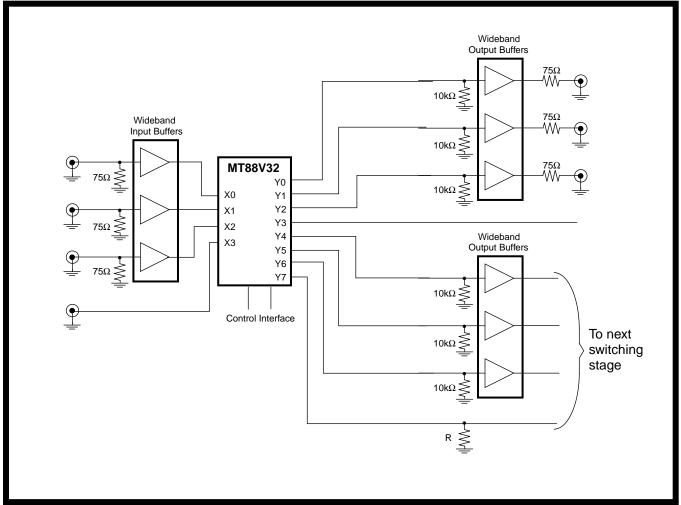

Figure 3 illustrates examples of how to connect the signal lines of the MT88V32 to various interfaces. Input buffers allow the incoming signals to be scaled and biased to the optimum operating range of the MT88V32 (i.e., differential phase error, differential gain error and  $R_{ON}$ ). Buffers will also allow a more precise input impedance to be implemented. For low grade video applications, signal lines may be connected directly, as long as the ultimate source and terminating impedances are matched.

Output buffers may be used to provide signal gain and impedance matching for external connections. Additionally, they may be used to isolate parasitic device capacitance in multiple stage switching applications where high frequency roll-off is critical. Crosstalk, as well as differential phase and gain error can be minimized by designing a low source impedance (e.g., 10 ohms), and a high terminating impedance (e.g., 10k) at each stage. If successive switching stages are not buffered, then a resistor to ground (R) should be present between the switches. Selection of R is based on the following compromise:

- 1) as R is decreased to approach the source and terminating resistance values signal loss will increase and crosstalk will decrease, and

- 2) as R increases signal loss will decrease and crosstalk will increase.

It is recommended that the power supply rails of the MT88V32 be decoupled with  $0.1\mu$ F ceramic Z5U and  $10\mu$ F dipped tantalum capacitors. These capacitors should be as close to the device as possible. The signal pins of the MT88V32 are interleaved with analog ground lines. This allows the circuit designer to run ground tracks on both sides of each signal line to improve crosstalk immunity.

The 8x4 bidirectional CMOS T-switch configuration is a modular switching element in a convenient package size. The inherent flexibility of this device permits the designer to build large switching matrices, see analog switch application notes.

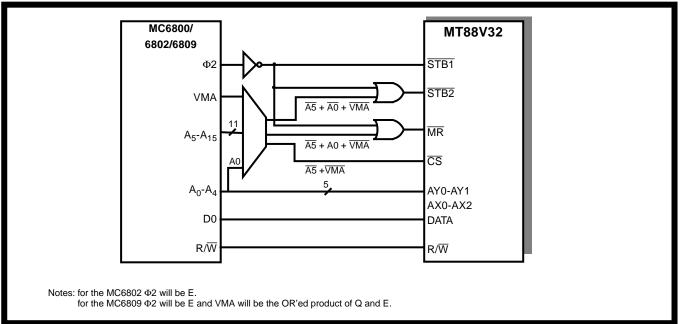

| А <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>0</sub>  | Function                                                                                    |

|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|---------------------------------------------------------------------------------------------|

| 0<br>↓<br>0    | 0<br>↓<br>1    | 0<br>↓<br>1    | 0<br>↓<br>1    | 0<br>↓<br>1    | 0<br>↓<br>1    | 1/0<br>↓<br>1/0 | $\begin{array}{c} \text{Y0 to X0} \\ \downarrow  \downarrow \\ \text{Y7 to X3} \end{array}$ |

| 1              | Х              | Х              | Х              | Х              | 0              | Х               | MR                                                                                          |

| 1              | Х              | Х              | Х              | Х              | 1              | Х               | STB2                                                                                        |

Table 3 - Address Decoding for the Processor Interfaces

Note: x = undefined, 1/0 -1 = make, 0 = break

Figure 3 - High Frequency Switching Applications

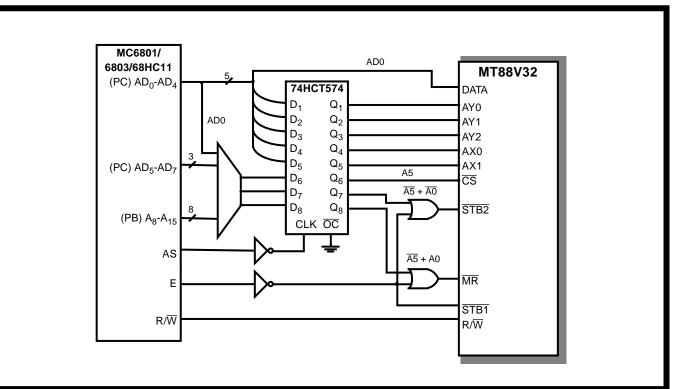

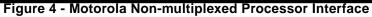

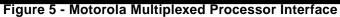

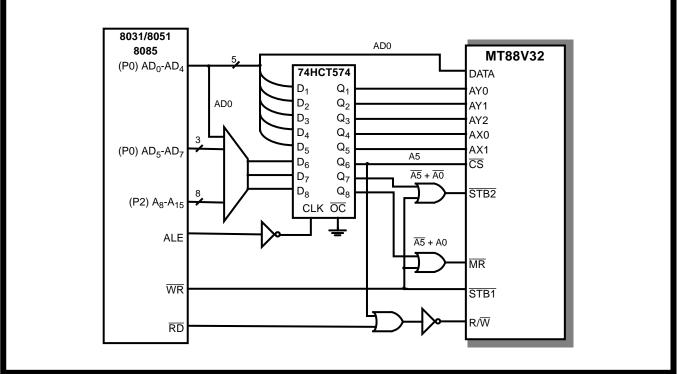

Figures 4, 5 and 6 show methods of interfacing the MT88V32 to Motorola and Intel microcontrollers. The address decoding for these configurations is in Table 3.

#### Video Signal Terminology

- Component Video separate red (R), blue (B), green (G), and synchronization signals.

- Composite Video contains luminance (brightness), chrominance (colour), and synchronization signal components in a single waveform.

- Synchronization signal horizontal sync pulses are negative going excursions of the composite video signal that occur every 63.5 μsec. Their function is to align the horizontal sweep.

Vertical synchronization is achieved during the vertical blanking interval, which is about 1200  $\mu$ sec or 20 horizontal scan intervals long. It consists of a number of vertical synchronization and equalization pulses.

- 4) Luminance is the black to white brightness component of a composite video signal. Its range is from reference white (maximum amplitude) to reference black (minimum amplitude).

- 5) Chrominance rides on the luminance signal and determines the hue (phase) and brightness (amplitude) of the colour component of a composite video signal.

- 6) Colour burst is about 9 (minimum 8) cycles of a 3.578545 MHz reference signal, which is transmitted with every horizontal sweep of the composite video signal. A phase comparison

Figure 6 - Intel Processor Interface

Figure 7 - Typical On-state Resistance (R<sub>ON</sub>) vs. DC Bias (Vdc) @ V<sub>DD</sub>=+5V, V<sub>EE</sub>=-7V

# MT88V32

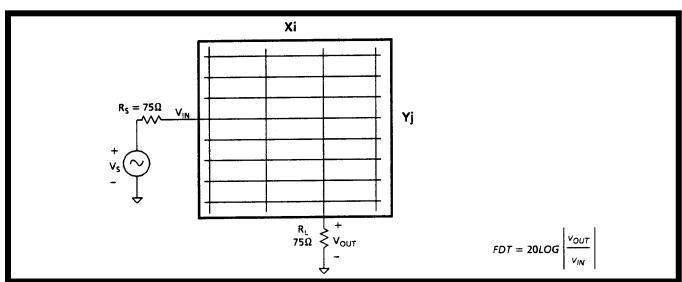

Figure 8 - Single Channel Feedthrough (all crosspoints open)

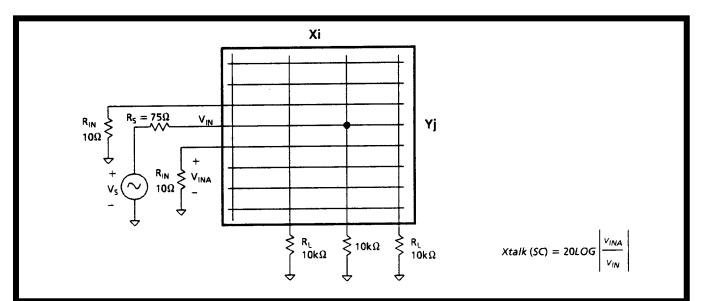

Figure 9 - Single Channel Crosstalk (one crosspoint closed)

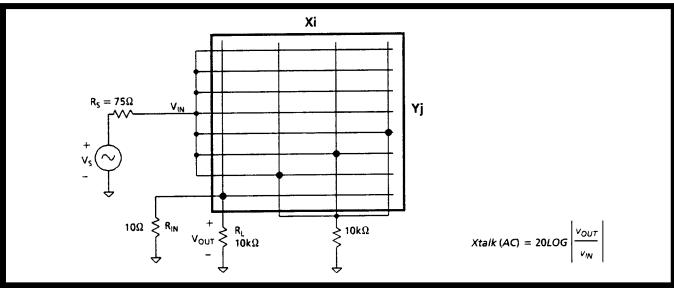

Figure 10 - All Channel Crosstalk (all crosspoints closed)

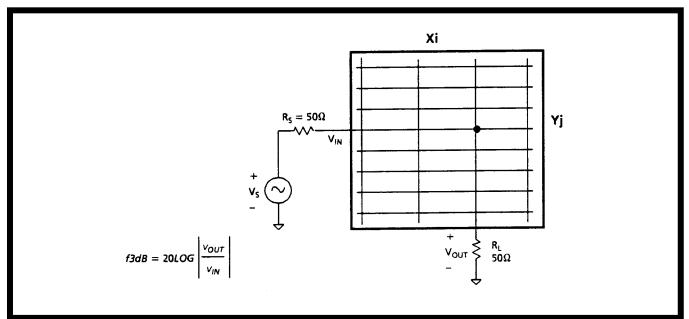

Figure 11 - 3dB Frequency Response

between this reference signal and the chrominance signal determines colour hue.

- 7) Differential Phase Error (measured in degrees) is a phase change in the chrominance signal due to a change in luminance amplitude.

- 8) Differential Gain Error (measured in percentage) is a change in amplitude of the chrominance signal due to a change in luminance amplitude.

Figure 13 - Typical Differential Gain vs. Ramp Voltage

#### Absolute Maximum Ratings\*- Voltages are with respect to V<sub>SS</sub> unless otherwise stated.

|   | Parameter                          |                                    | Symbol           | Min                  | Max                  | Units |

|---|------------------------------------|------------------------------------|------------------|----------------------|----------------------|-------|

| 1 | Supply Voltage                     | V <sub>DD</sub> to V <sub>SS</sub> |                  | -0.3                 | 15                   | V     |

|   |                                    | V <sub>DD</sub> to V <sub>EE</sub> |                  | -0.3                 | 15                   | V     |

|   |                                    | V <sub>SS</sub> to V <sub>EE</sub> |                  | -0.3                 | 15                   | V     |

|   |                                    | GND to V <sub>SS</sub>             |                  | V <sub>EE</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 2 | Analog Input Voltage               |                                    | V <sub>IN</sub>  | V <sub>EE</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 3 | Digital Input Voltage              |                                    | V <sub>IND</sub> | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 4 | Continuous Current (any analog I/C | ) terminal)                        |                  |                      | ±15                  | mA    |

| 5 | Storage Temperature                |                                    |                  | -65                  | +150                 | °C    |

| 6 | Operating Temperature              |                                    |                  | -40                  | +85                  | °C    |

| 7 | Package Power Dissipation          |                                    |                  |                      | 600                  | mW    |

\* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

#### Recommended Operating Conditions - Voltages are with respect to 0V unless otherwise stated.

|   | Characteristics                                                                     | Sym                                | Min             | Тур         | Max             | Units  | Test Conditions                                                                    |

|---|-------------------------------------------------------------------------------------|------------------------------------|-----------------|-------------|-----------------|--------|------------------------------------------------------------------------------------|

| 1 | Supply Voltage V <sub>DD</sub> -V <sub>EE</sub><br>V <sub>EE</sub> -V <sub>SS</sub> |                                    | 4.5<br>-8.5     | 12          | 13.2<br>0       | V<br>V |                                                                                    |

|   |                                                                                     | V <sub>DD</sub><br>V <sub>EE</sub> | 4.5<br>-8.5     | 5.0<br>-7.0 | 13.2<br>0       | V<br>V | V <sub>EE</sub> =V <sub>SS</sub> =0V<br>V <sub>DD</sub> =4.5V, V <sub>SS</sub> =0V |

| 2 | Analog Input Voltage                                                                | V <sub>IN</sub>                    | V <sub>EE</sub> |             | V <sub>DD</sub> | V      |                                                                                    |

| 3 | Digital Input Voltage                                                               | V <sub>IND</sub>                   | $V_{SS}$        |             | V <sub>DD</sub> | V      |                                                                                    |

| 4 | Analog Ground                                                                       | GND                                | $V_{EE}$        | 0           | $V_{DD}$        | V      |                                                                                    |

### DC Electrical Characteristics<sup>†</sup> Analog Switch Characteristics

Voltages are with respect to V<sub>DD</sub>=+5V, V<sub>EE</sub> =-7V, V<sub>SS</sub>=0V unless otherwise stated.

|   |                                   |                  | 25°C |     | 85°C |       | Test                                                                    |

|---|-----------------------------------|------------------|------|-----|------|-------|-------------------------------------------------------------------------|

|   | Characteristics                   | Sym              | Typ‡ | Мах | Max  | Units | Conditions                                                              |

| 1 | On-state Resistance               | R <sub>ON</sub>  |      |     |      |       | V <sub>IN</sub> =V <sub>DC</sub> =(V <sub>DD</sub> +V <sub>EE</sub> )/2 |

|   | V <sub>EE</sub> =-7V              |                  | 50   | 65  | 75   | Ω     |                                                                         |

|   | V <sub>EE</sub> =-5V              |                  | 60   | 75  | 85   | Ω     | $IV_{Xi}-V_{Yi}I = 0.4V$                                                |

|   | V <sub>EE</sub> =0V               |                  | 140  | 185 | 220  | Ω     | See Figure 7.                                                           |

| 2 | Difference in on-state resistance | $\Delta R_{ON}$  | 6    | 10  | 10   | Ω     | $IV_{Xi}-V_{Yi}I = 0.4V$                                                |

|   | between switches                  |                  |      |     |      |       | $V_{IN}=V_{DC}=(V_{DD}+V_{EE})/2$                                       |

| 3 | Off-state leakage current         | I <sub>OFF</sub> | ±10  |     | ±200 | nA    | V <sub>IN</sub> =V <sub>DD</sub> or V <sub>EE</sub>                     |

| 4 | On-state leakage current          | I <sub>ON</sub>  | ±10  |     | ±200 | nA    | $V_{IN}=V_{DD}$ or $V_{EE}$                                             |

† DC Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

‡ Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

# **DC Electrical Characteristics**<sup>†</sup>- **Power Supplies** - Voltages are with respect to $V_{DD}$ =+5V, $V_{EE}$ =-7V, $V_{SS}$ =0V, $\overline{MR}$ = 0.8V unless otherwise stated.

|   | Characteristics         | Sym             | Min | Тур‡ | Max | Units | Test Conditions                                             |

|---|-------------------------|-----------------|-----|------|-----|-------|-------------------------------------------------------------|

| 1 | Positive Supply Current | I <sub>DD</sub> |     | 1    | 100 | μA    | V <sub>IND</sub> =V <sub>DD</sub> or V <sub>SS</sub>        |

|   |                         |                 |     | 0.4  | 1.5 | mA    | V <sub>IND</sub> =2.4V                                      |

|   |                         |                 |     | 5    | 15  | mA    | V <sub>DD</sub> =12V, V <sub>SS</sub> =V <sub>EE</sub> =0V, |

|   |                         |                 |     |      |     |       | V <sub>IND</sub> =3.4V                                      |

| 2 | Negative Supply Current | I <sub>EE</sub> |     | 1    | 100 | μΑ    | V <sub>IND</sub> =V <sub>DD</sub> or V <sub>SS</sub>        |

|   |                         |                 |     | 1    | 100 | μA    | V <sub>IND</sub> =2.4V                                      |

|   |                         |                 |     | 1    | 100 | μA    | V <sub>DD</sub> =12V, V <sub>SS</sub> =V <sub>EE</sub> =0V, |

|   |                         |                 |     |      |     |       | $V_{DD}$ =12V, $V_{SS}$ = $V_{EE}$ =0V,<br>$V_{IND}$ =3.4V  |

† DC Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

‡ Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

# DC Electrical Characteristics<sup>†</sup> - Digital Input/Output

Voltages are with respect to  $V_{DD}$ =5V,  $V_{FF}$ =-7V,  $V_{SS}$ =0V, unless otherwise stated.

|   | Characteristics              | Sym               | Min             | Typ <sup>‡</sup> | Max             | Units | Test Conditions                                           |

|---|------------------------------|-------------------|-----------------|------------------|-----------------|-------|-----------------------------------------------------------|

| 1 | Input logic "1" level        | V <sub>IH</sub>   | 2               |                  |                 | V     |                                                           |

|   |                              | V <sub>IH</sub>   | 3.3             |                  |                 | V     | V <sub>EE</sub> =V <sub>SS</sub> =0, V <sub>DD</sub> =12V |

| 2 | Input logic "0" level        | VIL               |                 |                  | 0.8             | V     |                                                           |

|   |                              | VIL               |                 |                  | 0.8             | V     | V <sub>EE</sub> =V <sub>SS</sub> =0, V <sub>DD</sub> =12V |

| 3 | Input leakage (digital pins) | I <sub>LEAK</sub> |                 | ±1               | ±10             | μA    | V <sub>IND</sub> =V <sub>DD</sub> or V <sub>SS</sub>      |

| 4 | Data output high voltage     | V <sub>OH</sub>   | 2.4             |                  | V <sub>DD</sub> | V     | I <sub>OH</sub> =7mA@V <sub>OH</sub> =2.4V                |

| 5 | Data output high current     | I <sub>OH</sub>   | 7               | 20               |                 | mA    | source V <sub>OH</sub> =2.4V                              |

| 6 | Data output low voltage      | V <sub>OL</sub>   | V <sub>SS</sub> |                  | 0.4             | V     | I <sub>OL</sub> =2mA@V <sub>OL</sub> =0.4V                |

| 7 | Data output low current      | I <sub>OL</sub>   | 2               | 5                |                 | mA    | sink V <sub>OL</sub> =0.4V                                |

| 8 | Data high impedance leakage  | I <sub>OZ</sub>   |                 | 1                | 10              | μA    | V <sub>O</sub> =0 to V <sub>DD</sub>                      |

† DC Electrical Characteristics are over recommended temperature range and recommended power supply voltages.

<sup>‡</sup> Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

Algebraic convention is adopted in this data sheet where the most negative value is a minimum and the most positive value is a maximum.

### AC Electrical Characteristics<sup>†</sup> - Crosspoint Performance- Voltages are with respect to V<sub>DD</sub>=+5V, V<sub>DC</sub>=0,

$V_{EE}$ =-7V,  $V_{SS}$ =0V, unlesss otherwise stated. Also applicable for  $V_{EE}$ = $V_{SS}$ =0,  $V_{DD}$ =+12V,  $V_{DC}$ =( $V_{DD}$ + $V_{EE}$ )/2.

|    | Characteristics                                                        | Sym                       | Min | Typ <sup>‡</sup> | Max | Units    | Test Conditions                                                                                                   |

|----|------------------------------------------------------------------------|---------------------------|-----|------------------|-----|----------|-------------------------------------------------------------------------------------------------------------------|

| 1  | On-state Xi capacitance                                                | C <sub>Xi (on)</sub>      |     |                  | 56  | pF       | 1 Xi to 1 Yi                                                                                                      |

| 2  | On-state Yi capacitance                                                | C <sub>Yi (on)</sub>      |     |                  | 56  | pF       | 1 Yi to 1 Xi                                                                                                      |

| 3  | Off-state Xi capacitance                                               | C <sub>Xi (off)</sub>     |     |                  | 30  | pF       |                                                                                                                   |

| 4  | Off-state Yi capacitance                                               | C <sub>Yi (off)</sub>     |     |                  | 15  | pF       |                                                                                                                   |

| 5  | Break-before-Make interval                                             | t <sub>open</sub>         |     | 10               |     | ns       |                                                                                                                   |

| 6  | Single channel feedthrough<br>(all crosspoints open)<br>(see Fig. 8)   | FDT                       |     | -80<br>-62       |     | dB<br>dB | R <sub>S</sub> = R <sub>L</sub> =75Ω<br>V <sub>IN</sub> =0.6Vpp @ 5MHz<br>V <sub>IN</sub> =0.6Vpp @ 15MHz         |

| 7  | Single channel feedthrough<br>(all crosspoints closed)<br>(See Fig. 9) | X <sub>talk</sub><br>(sc) |     | -85<br>-68       |     | dB<br>dB | R <sub>IN</sub> = 10Ω, R <sub>L</sub> = 10kΩ<br>V <sub>IN</sub> =0.6Vpp @ 5MHz<br>V <sub>IN</sub> =0.6Vpp @ 15MHz |

|    |                                                                        | X <sub>talk</sub><br>(sc) |     | -70<br>-50       |     | dB<br>dB | R <sub>IN</sub> = 75Ω, R <sub>L</sub> = 10kΩ<br>V <sub>IN</sub> =0.6Vpp @ 5MHz<br>V <sub>IN</sub> =0.6Vpp @ 15MHz |

| 8  | All channel crosstalk<br>(all crosspoints closed)<br>(See Fig. 10)     | X <sub>talk</sub><br>(ac) |     | -55              |     | dB       | R <sub>IN</sub> = 10Ω, R <sub>L</sub> = 10kΩ<br>V <sub>IN</sub> =0.6Vpp @ 5MHz                                    |

| 9  | Frequency Response<br>(see Fig.11)                                     | f <sub>3dB</sub>          |     | 200              |     | MHz      | $R_S = R_L = 50\Omega$                                                                                            |

| 10 | Differential Phase Error                                               | DP                        |     | 0.05             |     | 0        | See NoteD, $R_S = 50\Omega$ , $R_L = 75\Omega$                                                                    |

| 11 | Differential Gain Error                                                | DG                        |     | 0.11             |     | %        | See Note $\mathbb{D}$ R <sub>S</sub> = 50 $\Omega$ ,<br>R <sub>L</sub> = 75 $\Omega$                              |

† Timing is over recommended temperature range.

‡ Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

#### Notes:

D Valid for V<sub>EE</sub>=-7V, V<sub>DD</sub>=+5V and V<sub>DC</sub>=-2.0V. Error will increase slightly if input is biased differently.

Input test signal: 700mV ramp biased @ -2.0Vdc with a superimposed video signal of 285Vrms @ 3.58 MHz.

Decision and Characterization and not subject to production testing.

### AC Electrical Characteristics<sup>†</sup> - Timing Characteristics- Voltages are with respect to V<sub>DD</sub>=+5V, V<sub>EE</sub>=-7V, $V_{SS}\text{=}0V\text{, }R_{L}\text{=}1k\Omega\text{, }C_{L}\text{=}50\text{pF}\text{ unlesss otherwise stated. Also applicable for }V_{EE}\text{=}V_{SS}\text{=}0\text{, }V_{DD}\text{=}\text{+}12V\text{.}}$

|    | Characteristics                                                                                   | Sym                                   | Min | Typ‡       | Max        | Units    | Test Conditions              |

|----|---------------------------------------------------------------------------------------------------|---------------------------------------|-----|------------|------------|----------|------------------------------|

| 1  | DATA to STROBE1 setup                                                                             | t <sub>ds1</sub>                      | 20  |            |            | ns       | t <sub>dh1 = 20ns min.</sub> |

| 2  | DATA to STROBE1 hold                                                                              | t <sub>dh1</sub>                      | 10  |            |            | ns       | t <sub>ds1 = 30ns</sub> min. |

| 3  | CS to STROBE1 setup                                                                               | t <sub>css1</sub>                     | 20  |            |            | ns       |                              |

| 4  | CS to STROBE1 hold                                                                                | t <sub>csh1</sub>                     | 20  |            |            | ns       |                              |

| 5  | ADDRESS to STROBE1 setup                                                                          | t <sub>ass1</sub>                     | 20  |            |            | ns       |                              |

| 6  | ADDRESS to STROBE1 hold                                                                           | t <sub>ash1</sub>                     | 20  |            |            | ns       |                              |

| 7  | STROBE1 pulse width                                                                               | t <sub>spw1</sub>                     | 75  |            |            | ns       |                              |

| 8  | STROBE2 pulse width                                                                               | t <sub>spw2</sub>                     | 75  |            |            | ns       |                              |

| 9  | R/W to STROBE1 setup                                                                              | t <sub>rwss1</sub>                    | 20  |            |            | ns       |                              |

| 10 | R/W to STROBE1 hold                                                                               | t <sub>rwsh1</sub>                    | 10  |            |            | ns       |                              |

| 11 | RESET pulse width                                                                                 | t <sub>rpw</sub>                      | 75  |            |            | ns       |                              |

| 12 | $\overline{\text{CS}}$ to High Z                                                                  | t <sub>rpw</sub>                      | 10  |            |            | ns       |                              |

| 13 | $\overline{\text{CS}}$ to DATA output valid                                                       | t <sub>csov</sub>                     |     |            | 200        | ns       |                              |

| 14 | STROBE2 to STROBE1 setup                                                                          | t <sub>s2s1</sub>                     | 0   |            |            | ns       |                              |

| 15 | STROBE1 to STROBE2 setup                                                                          | t <sub>s1s2</sub>                     | 0   |            |            | ns       |                              |

| 16 | MR to switch OPEN delay 50% MR to10% Output                                                       | t <sub>rst</sub>                      |     |            | 300        | ns       |                              |

| 17 | $R/\overline{W}$ to DATA output valid                                                             | t <sub>rwov</sub>                     |     |            | 150        | ns       |                              |

| 18 | Address to DATA output valid                                                                      | t <sub>aov</sub>                      |     |            | 200        | ns       |                              |

| 19 | $R/\overline{W}$ to High Z                                                                        | t <sub>rwz</sub>                      | 10  |            |            | ns       |                              |

| 20 | Address to High Z                                                                                 | t <sub>az</sub>                       | 10  |            |            | ns       |                              |

| 21 | STROBE2 to switch status delay<br>50% strobe to10% output change<br>tstrobe2(on)<br>tstrobe2(off) | t <sub>son</sub><br>t <sub>soff</sub> |     | 100<br>100 | 300<br>300 | ns<br>ns |                              |

† Timing is over recommended temperature range with V<sub>IH</sub>=5V, V<sub>IL</sub>=0V, V<sub>OH</sub>=2.4V, V<sub>OL</sub>=0.8V, R<sub>L</sub>=3kΩ (DATA) and R<sub>L</sub>=1kΩ (analog).

‡ Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

# MT88V32

Figure 14 - Write Cycle Timing Diagram

Figure 15 - Read Cycle Timing Diagram